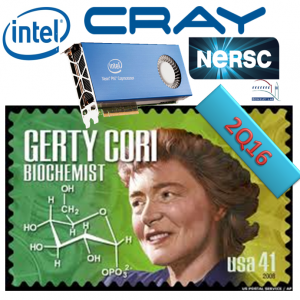

Scheduled for delivery in mid-2016, NERSC‘s next-generation supercomputer, a Cray XC, will be named after Gerty Cori, the first American woman to be honored with a Nobel Prize in science. The Cory supercomputer will use Intel’s next-generation Intel® Xeon Phi™ processor –- code-named “Knights Landing” — a self-hosted, manycore processor with on-package high bandwidth memory and delivers more than 3 teraFLOPS of double-precision peak performance per single socket node.

The Cori the supercomputer will have over 9300 Knights Landing compute nodes – or approximately 27.9 PF/s double-precision KNL performance – and provide over 400 gigabytes per second of I/O bandwidth and 28 petabytes of disk space. The contract also includes an option for a “Burst Buffer,” a layer of NVRAM that would move data more quickly between processor and disk

This procurement places a clear delivery date for the Knights-landing processor.

As noted on techEnablement.com, this hardware should run force calculations for biochemical systems quite well using exaFMM – along with machine-learning and numerical optimization problems.

The full public information from Intel about the Knights Landing chip is:

- Knights Landing is the code name for the 2nd generation product in the Intel® Many Integrated Core Architecture

- Knights Landing targets Intel’s 14 nanometer manufacturing process

- Knights Landing will be productized as a processor (running the host OS) and a coprocessor (a PCIe end-point device)

- Knights Landing will feature on-package, high-bandwidth memory

- Flexible memory modes for the on package memory include: flat, cache, and hybrid modes

- Knights Landing will support Intel® Advanced Vector Extensions AVX-512, details of which are already published.

Intel notes that any information beyond that is rumor and speculation which Intel cannot confirm or deny.

That said there is more on the web about the 72-core Knights Landing chip such as the information on Extreme Tech.

Thanks to Cary Whitney on Google+!

Leave a Reply